深入理解计算机系统第4章笔记

处理器体系结构

1.ISA:指令集体系结构,是指一个处理器支持的指令和指令的字节级编码

2.ISA在编译器编写者和处理器设计人员之间提供了一个概念抽象层,编译器编写者只需要知道允许哪些指令,以及它们是如何编码 的;而处理器设计者必须建造出执行这些指令的处理器

3.ISA模型看上去应该是顺序指令执行,也就是先取出一条指令,等到它执行完毕,再开始下一条.然而,与一个时刻只执行一条指令 相比,通过同时处理金条指令的不同部分,处理器可以获得较高的性能(流水线),为了保证处理器能达到同顺序执行相同的结果,人 们采用了一些特殊的机制

4.生产处理器的公司很少,但是研究处理器的设计人员的队伍已经非常巨大了,而且还在增大.一个主要的处理器设计的各个方面大 约涉及1000多人

5.HCL:硬件控制语言,是一种描述硬件系统控制部分的简单语言

6.基于顺序操作的功能正确但是有点不实用的Y86处理器是作者用的例子,基于这个顺序设计为基础,进行一系列的改造,创建一个 流水线化的处理器,这个流水线化的处理器将每条指令的执行分解成五步,处理器可以同时执行五条指令的不同阶段,为了使这个处 理器保留Y86 ISA的顺序的性质,要求处理很多冒险或冲突情况,冒险就是一条指令的位置或操作数信赖于其他仍在流水线中的指令

7.指令集的一个重要性质就是字节编码必须有唯一的解释,任意一个字节序列要么是一个唯一的指令序列的编码,要么就不是一个 合法的字节序列

8.通过将逻辑门组合成大的网,可以构造出能计算更加复杂函数的组合电路.算术/逻辑单元(ALU)是一种很重要的组合电路

9.cpu的时钟频率也即工作频率,一般来说,一个时钟周期内完成的指令数是固定的,所以时钟频率越高,cpu的速度也就越快了,为什 么要有时钟可参考”通俗易懂的例子,好吧,分析一下抬轿子,八抬大轿,轿夫要一起用力,用力的方向和时间需一致,移轿中每 人的行进方向和速率也要一致,轿夫头负责喊号子,他的行动和速度是其它七个人的参照基点,这个轿夫头在某种意义上就是时 钟,没有这个轿夫头,八个人各行其事,轿子是无法到达目的地的,甚至都不能被抬离地面.” 4G的处理器表示这个处理器的时钟运行 频率是4GHz

10.时钟寄存器存储单个位或字.时钟信号控制寄存器加载输入值.时钟信号上升时,输出=输入,时钟信号未上升时,输出=当前状态

11.SEQ(“sequential”顺序的)处理器:每个时钟周期上,SEQ执行处理一条完整指令所有步骤.SEQ唯一的问题就是它太慢了.时钟必 须非常慢,以使信号能在一个周期内传播所有的阶段.SEQ的实现包括组合逻辑和两种存储器设备:时钟寄存器(程序计数器和条件码 寄存器),随机访问存储器(寄存器文件,指令存储器和数据存储器).组合逻辑不需要任何时序或控制——只要输入变化了,值就通 过逻辑门网络传播.SEQ这种方法不能充分利用硬件单元,因为每个单元只在整个时钟周期的一部分时间内才被使用,使用流水线可 获得更好的性能,流水线化的一个重要特性就是增加了系统的吞量,也就是单位时间内服务的顾客总数.

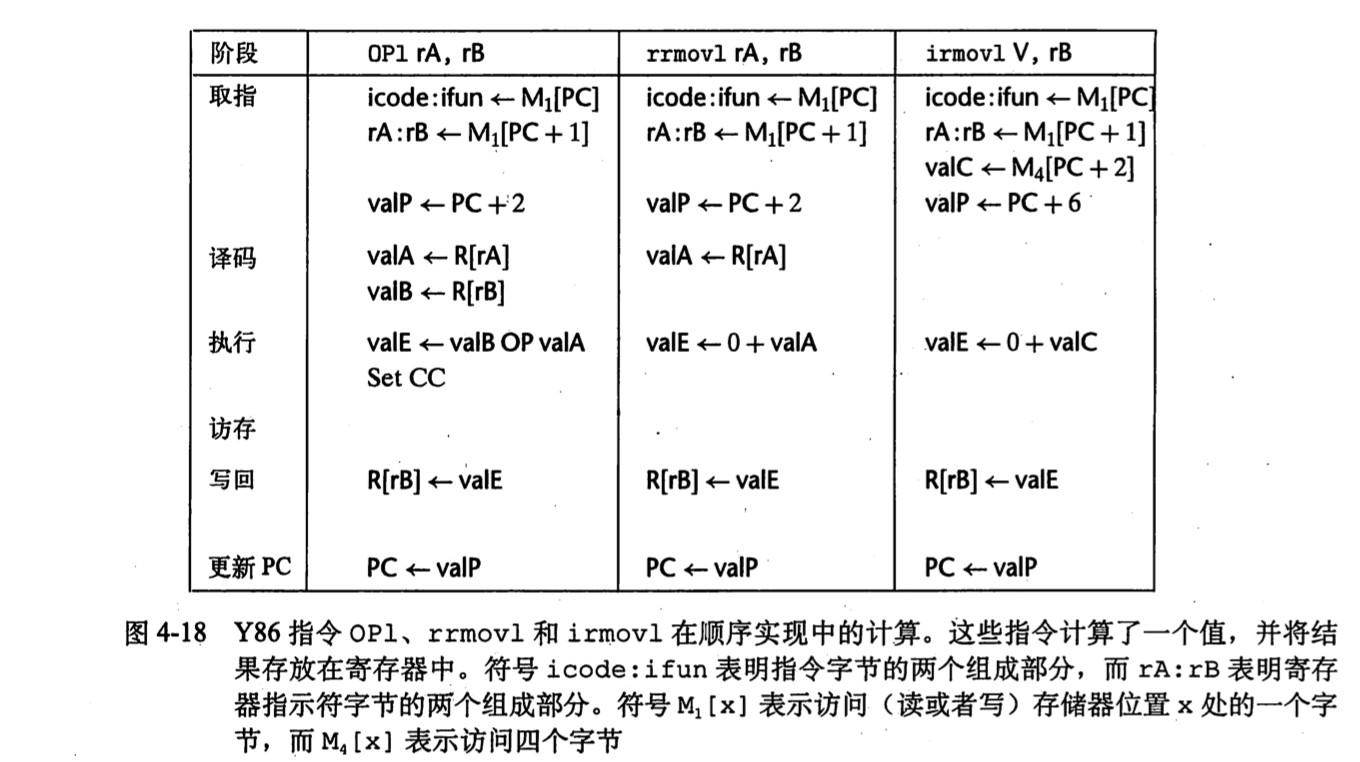

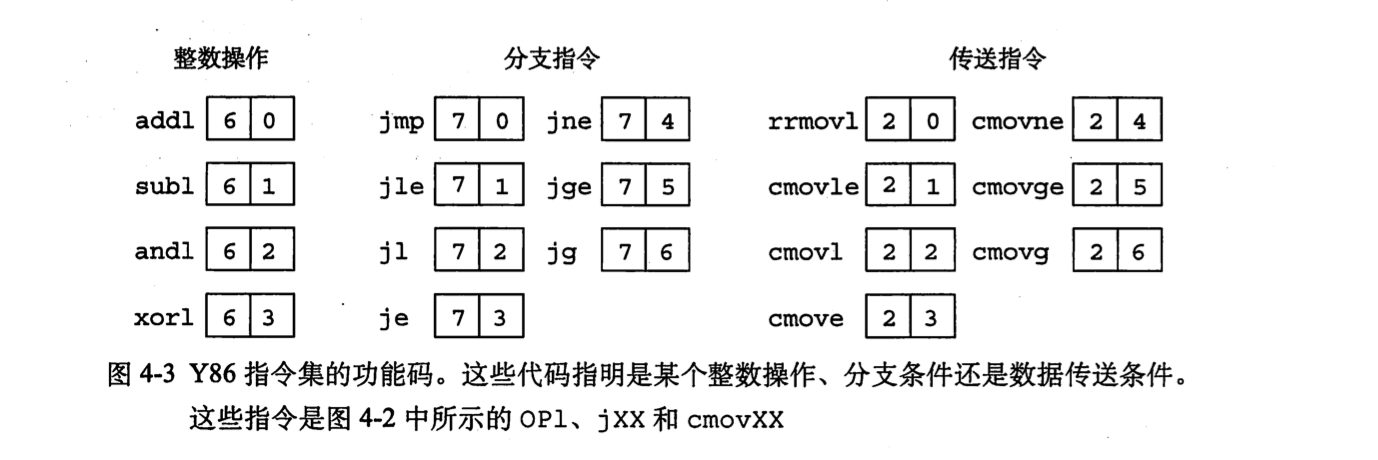

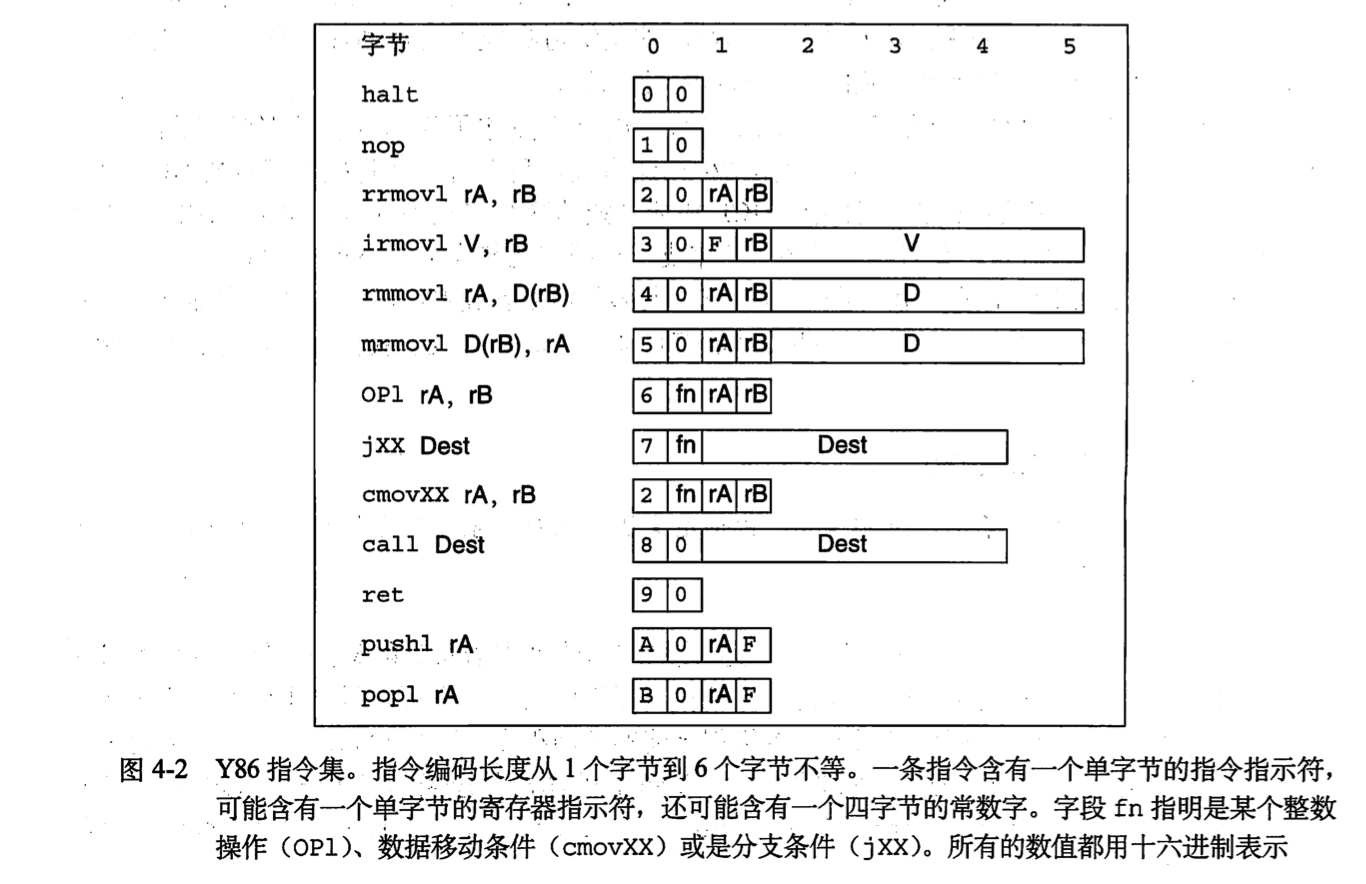

12.指令的字节级编码如下图4-3,每条指令需要1-6个字节不等,每条指令的第一个字节表明指令的类型,这个字节分为两个部分:高 4位和低4位,高4位是代码(code)部分,低4位是功能(function)部分.如下图4-2中,代码值为0-0xB,功能值只有在一组相关指令共用 一个代码时才有用.

13.实现所有Y86指令所需要的计算可以组织成六个阶段:取指,译码,执行,访存,写回,更新pc. 取指:从程序计数器(PC)中读取指令指示符字节的两个四位部分,称为icode(指令代码)和ifun(指令功能) 译码:从寄存器文件读入最多两个操作数,得到值valA和/或valB. 执行:算术/逻辑单元(ALU)要么执行指令指明的操作(根据ifun的值),计算存储器引用的有效地址,要么增加或减少栈指针.得到的 值称为valE 访存:将数据写入存储器或从存储器读出数据,读出的值为valM 写回:最多可以写两个结果到寄存器文件 更新PC:将PC设置成下一条指令的地址

如下图4-18是对OP1(整数和逻辑运算),rrmov1(寄存器-寄存器传送)和irmov1(立即数-寄存器传送)类型的指令所需的处理